IV. MONOSTABLE A CIRCUIT INTEGRE NE555

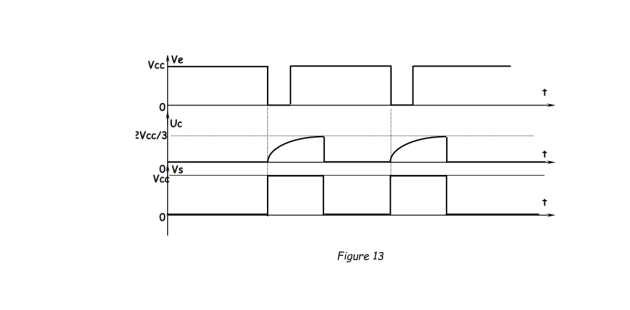

1. Schéma du montage à étudier

2. Fonctionnement

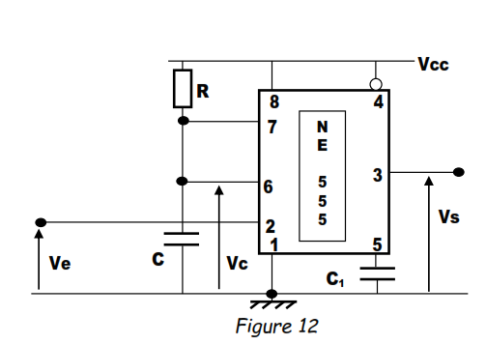

2.1. État stable ou de repos

A l'instant t0, Vs = 0 → le transistor interne est saturé . Le condensateur est déchargé. Ve est à l'état haut→ Vc = 0.

L'impulsion de déclenchement (tension inférieure à Vcc/3) appliquée à la borne 2 met le bistable interne en position « charge », ce qui bloque le transistor ; la sortie est à l'état haut.

2.2. État instable

Le transistor étant bloqué, le condensateur C se charge à travers la résistance R selon la loi : Uc = Vcc(1-e-t/RC) jusqu'à ce que Uc = Vréf = 2Vcc/3.

2.3. Phase de récupération

Dés que Uc = Vréf = 2Vcc/3, le comparateur 1 interne (voir cour sur les astables) change d'état et ramène le bistable interne dans sa fonction initiale, ce qui entraîne la saturation du transistor et la décharge instantanée du condensateur. La sortie passe au niveau bas (Vs = 0).

2.3. Les chronogrammes

2.4. Calcul de la période propre T0

![]() . Avec Uf = VCC ; Ui = 0 ; U0 =2 VDD/3

. Avec Uf = VCC ; Ui = 0 ; U0 =2 VDD/3

Ce qui donne :T0 = τln3 = RCln3

2.5. Vidéo simulation